- 您现在的位置:买卖IC网 > Sheet目录3818 > PIC18F4620-I/ML (Microchip Technology)IC MCU FLASH 32KX16 44QFN

PIC17C4X

DS30412C-page 104

1996 Microchip Technology Inc.

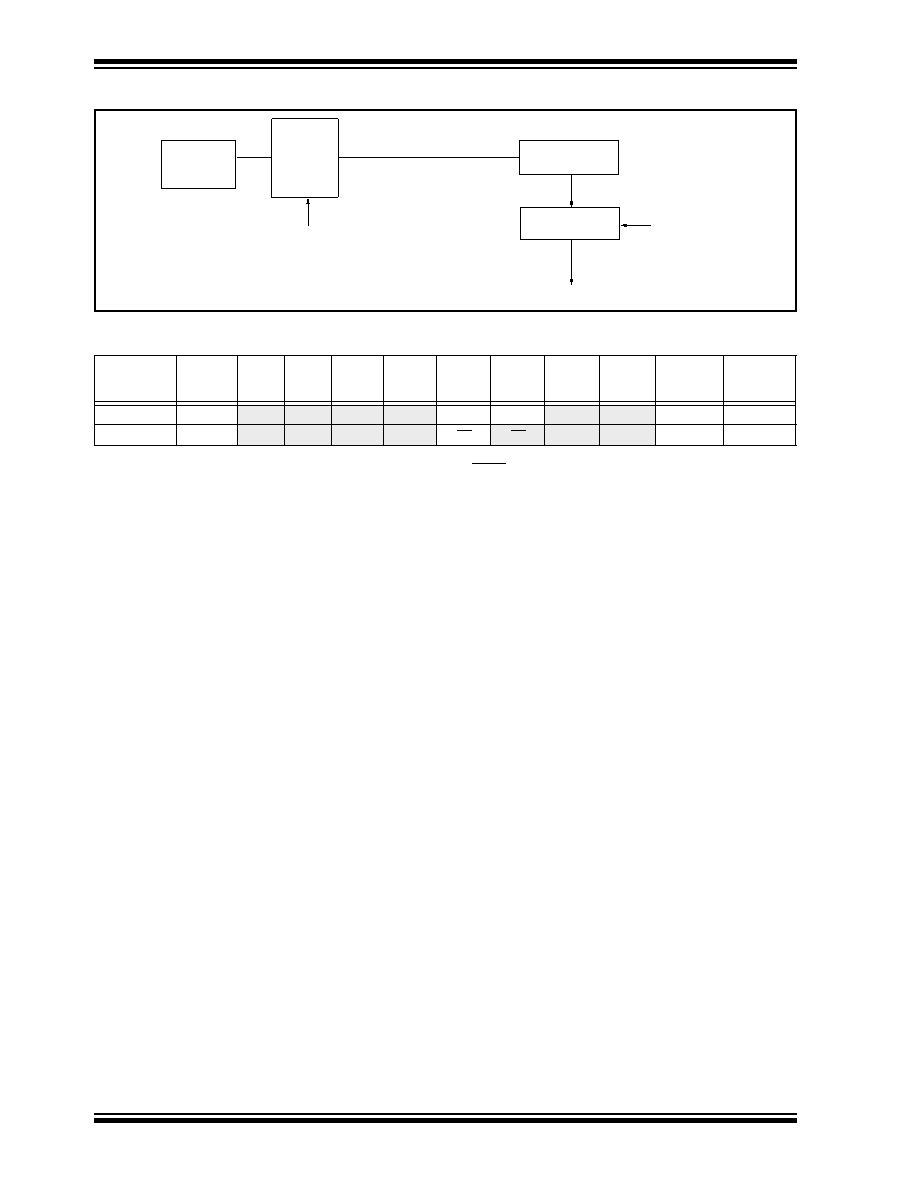

FIGURE 14-8: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 14-4:

REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

Power-on

Reset

Value on all

other resets

(Note1)

—

Cong

—

PM1

—

PM0

WDTPS1

WDTPS0

FOSC1

FOSC0

(Note 2)

06h, Unbanked

CPUSTA

—

STKAV

GLINTD

TO

PD

—

--11 11--

--11 qq--

Legend: - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by the WDT.

Note 1:

Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

2:

This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

WDT

WDT Enable

Postscaler

4 - to - 1 MUX

WDTPS1:WDTPS0

On-chip RC

WDT Overow

Oscillator(1)

Note 1: This oscillator is separate from the external

RC oscillator on the OSC1 pin.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24HJ256GP210-I/PT

IC PIC MCU FLASH 128KX16 100TQFP

PIC24HJ128GP310A-I/PF

IC PIC MCU FLASH 128KB 100-TQFP

DSPIC33FJ128GP310-I/PF

IC DSPIC MCU/DSP 128K 100TQFP

PIC16C66-20I/SO

IC MCU OTP 8KX14 PWM 28SOIC

DSPIC33FJ128MC510-I/PT

IC DSPIC MCU/DSP 128K 100TQFP

PIC16C66-20I/SP

IC MCU OTP 8KX14 PWM 28DIP

PIC18LF2620-I/SP

IC MCU FLASH 32KX16 28SDIP

PIC16F877-04I/P

IC MCU FLASH 8KX14 EE 40DIP

相关代理商/技术参数

PIC18F4620-I/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 DIP40

PIC18F4620-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 TQFP44

PIC18F4620T-I/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620T-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4680-E/ML

功能描述:8位微控制器 -MCU 64KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4680-E/P

功能描述:8位微控制器 -MCU 64KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT